MOS晶体管结构和工作原理的文章,必看

信息来源:本站 日期:2017-08-08

_按沟道区中载流子类型分

N沟MOS晶体管:衬底为P型,源漏为重掺杂的N+,沟道中 载流子为电子

P沟MOS晶体管:衬底为N型,源漏为重掺杂的P+,沟道中载流子为空穴

在正常情况下,只有一种类型的载流子在工作,因此也称其为单极晶体管

-按工作模式分

增强型晶体管:若在零栅压下不存在漏源导电沟道,为了形成导电沟道,需要施加一定的栅压,也就是说沟道要通过“增强”才能导通

耗尽型晶体管:器件本身在漏源之间就存在导电沟道,即使在零栅压下器件也是导通的。若要使器件截止,就必须施加栅压使沟道耗尽

假定漏端电压Vds为正,当栅上施加一个小于开启电压的正栅压时,栅氧下面的P型表面区的空穴被耗尽,在硅表面形成一层负电荷,这些电荷被称为耗尽层电荷Qb。这时的漏源电流为泄漏电流。

如果Vgs>Vth,在P型硅表面形成可移动的负电荷Qi层,即导电沟道。

由于表面为N型的导电沟道与P型衬底的导电类型相反,因此该表面导电沟道被称为反型层。

当衬底施加偏压时,势垒高度的增加导致耗尽区宽度的增加,因此对于给定的Vgs和Vds,Vbs的增加会使Ids减小。这是因为Vbs增加,体电荷Qb增加,而Vgs和Vds不变,由于栅电荷Qg固定,根据电荷守恒定律Qg=Qi+Qb,所以Qi反型层电荷减少,因此电导减少。

而这时,如果要使MOS晶体管开启即进入强反型区,就是反型层电荷相应的增加那就耍提高栅电压,增加栅电荷。所以当MOS衬底施加偏压时,MOS晶体管的开启电压会升高。

当沟道长度减小,同时保持电源电压不变,沟道区靠近漏端附近的最大电场增加。随着载流子从源向漏移动,它们在漏端高电场区将得到足够的动能,引起碰撞电离,一些载流子甚至能克服Si-Si02界面势垒进入氧化层,这些高能载流子不再保持它们在晶格中的热平衡状态,并且具高于热能的能量,因此称它们为热载流子。对于正常工作中的MOSFET,沟道中的热载流子引起的效应称为热载流子效应。

当发生碰撞时,热载流子将通过电离产生次级电子一空穴对,其中电子形成了从漏到源的电流,碰撞产生的次级空穴将漂移到衬底区形成衬底电流Ib。通过测量Ib可以很好地监控沟道热载流子和漏区电场的情况。

由于Si-Si02的界面势垒较高,注入到栅氧化层中的热载流子与碰撞电离产生的热载流子相比非常少,因此栅电流比衬底电流要低几个数量级。

热载流子注入到栅氧层中还会引起其它的一些效应,主要有

(1)热载流子被Si02中电激活的缺陷俘获,是氧化层中的固定电荷密度Qot改变; (2)在Si-Si02界面产生界面电荷Qit。由于Qot和Qit引起的电荷积累将在沟道形成阻碍载流子运动的势垒;同时界面电荷也会增强界面附近电子的库仑散射,使迁移率降低。因此经过一段时间的积累,以上效应会使器件的性能退化,影响集成电路的可靠性,所以应设法避免热载流子效应。

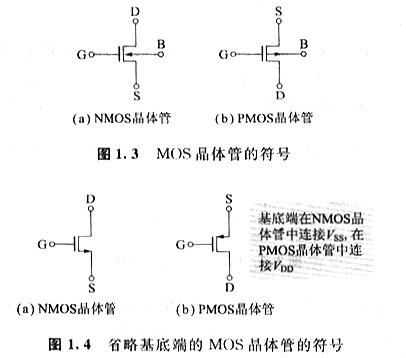

MOS晶体管的符号示于图1.3。(KIA)MOS晶体管是四端器件:源极(S)、栅极(G)、漏极(D),以及基底端(B)。基底端在NMOS晶体管中通常衔接电路的负端电源电压Vss,在PMOS晶体管中衔接电路的正端电源电压VDD。电路图中通常省略基底端(B)而采用图1.4所示的符号。两者的关系如图1.5所示。

图1.6是NMOS晶体管的构造表示图。P型硅衬底上构成两个n+区域,一个是源区,另一个是漏区。栅极是由掺入高浓度杂质的低电阻多晶硅(poly-crystal-linc silicon)构成。

在栅极与硅衬底间构成一层氧化膜( Si02),叫做栅氧化膜。P型硅衬底也叫做基板。

NMOS的基底衔接VSS负端电源电压。例如,在正的电源电压VDD为3V,负的电源电压VSS为OV的电路中工作时,基底衔接OV(图1.7)。

画电路图时,NMOS晶体管是漏极在上、源极在下,而PMOS晶体管是源极在上、漏极在下。图1.8示出电流活动的方向和电极间的电压。栅极—源极间电压用VGS(PMOS晶体管中用VSG)表示,漏极—源极间电压用VDS(PMOS晶体管中VSD)表示。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

关注KIA半导体工程专辑请搜微信号:“KIA半导体”或点击本文下方图片扫一扫进入官方微信“关注”

长按二维码识别关注